- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

C906 RISC-V-kort

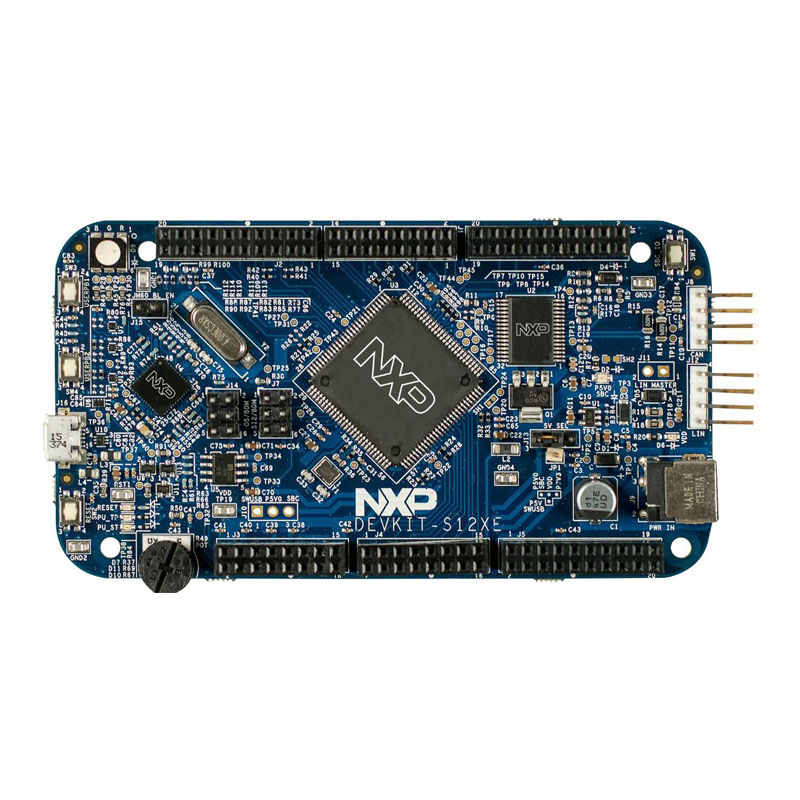

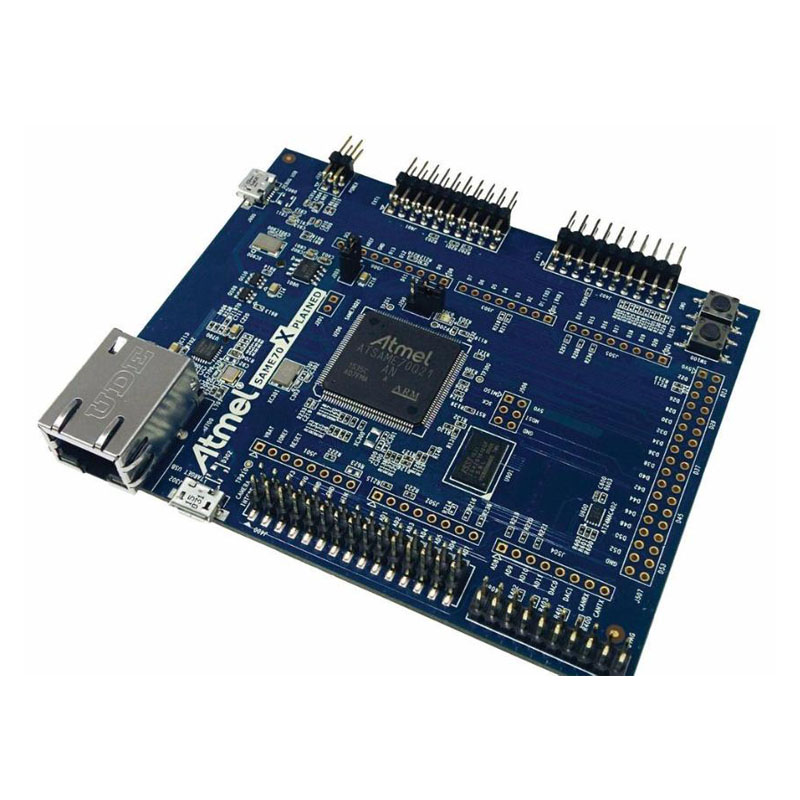

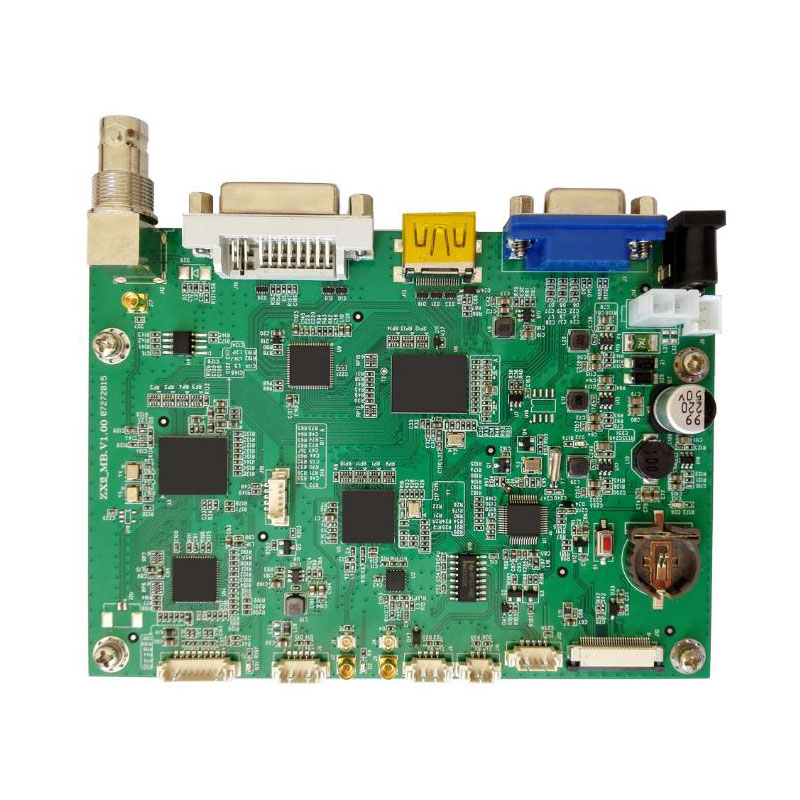

C906 RISC-V Board design, utveckling och tillverkning är huvudspecialiteterna för Ningbo Hi-tech Easy Choice Technology Co., Ltd:s högteknologiska verksamhet. Vår verksamhet har ett fantastiskt rykte för att tillhandahålla utmärkt service, odla långvariga allianser med framstående företag, statliga organisationer och en ansenlig användarbas. Våra specialområden inkluderar utvecklingen av kompletta intelligenta elektroniska styrkort, design av mekaniska och elektriska styrprodukter, skapandet av mikrodatorer med ett chip, kretsdesign och testtjänster efter produktion. Vi har kapaciteten att utveckla styrkretsar som är skräddarsydda efter dina behov, för att levandegöra funktionaliteten hos din önskade produkt, oavsett om du erbjuder oss med detaljerade funktionsspecifikationer eller bara en vag idé.

Skicka förfrågan

YCTECHs industriella produktstyrkortsutveckling inkluderar industriell styrkortsmjukvarudesign, mjukvaruuppgradering, schematiskt diagramdesign, PCB-design, PCB-produktion och PCBA-bearbetning belägen på Kinas östkust. Vårt företag designar, utvecklar och tillverkar C906 RISC-V-kort. Ali Group Pingtouge har successivt lanserat flera RISCV-processorer, och några processorer har använts i branschen. Till exempel, i en viss Zhis D1-processor är Pingtouges Xuantie C906-kärna inbäddad som "kärnan". Även om RISCV är en öppen standard och det finns vissa RTL-implementeringar av kärnor med öppen källkod på Internet, är kommersiella RISCV-kärnor i allmänhet sluten källkod. Men det som är förvånande är att Brother Pingtou i oktober i år köpte de fyra RISCV-kärnor som han designade, inklusive C906-kärnan som används av D1.

Xuantie C906 är en processorkärna för 64-bitars RISC-V-arkitektur till låg kostnad utvecklad av Alibaba Pingtouge Semiconductor Co., Ltd. Xuantie C906 är baserad på 64-bitars RISC-V-arkitekturen och har utökat och förbättrat RISC-V-arkitekturen. Utökade förbättringar inkluderar:

1. Förbättring av instruktionsuppsättningen: Fokusera på fyra aspekter av minnesåtkomst, aritmetiska operationer, bitoperationer och Cache-operationer, och totalt 130 instruktioner har utökats. Samtidigt stödjer Xuantie-processorutvecklingsteamet dessa instruktioner på kompilatornivå. Förutom Cache-operationsinstruktionerna kan dessa instruktioner kompileras och genereras, inklusive GCC- och LLVM-kompilering.

2. Förbättring av minnesmodell: Utöka minnessideattribut, stöd sidattribut som Cacheable och Strong order, och stöd dem på Linux-kärnan.

Viktiga arkitektoniska parametrar för Xuantie C906 inkluderar:

RV64IMA[FD]C[V] arkitektur

Pingtouge instruktion expansion och förbättringsteknik

Teknik för förbättring av Pingtouge minnesmodell

5-stegs heltalspipeline, sekventiell exekvering i en fråga

128-bitars vektorberäkningsenhet, stöder SIMD-beräkning av FP16/FP32/INT8/INT16/INT32.

C906 är en RV64-bitars instruktionsuppsättning, 5-nivås sekventiell enkelstart, 8KB-64KB L1 Cache-stöd, inget L2 Cache-stöd, halv/enkel/dubbel precisionsstöd, VIPT fyrvägskombination L1-datacache.